한계를 뛰어넘는 원자 수준의 정밀도 제어

오늘날 최첨단 칩 제조에 사용되는 반도체 공정에는 원자 수준의 정밀 제어가 필요합니다. 나노급 피처, 신소재, 점점 복잡해지는 3D 구조로 물리적, 화학적 한계를 뛰어넘어야 하는 상황에 직면해 있기 때문입니다. 원자 수준의 정밀 제어는 끊임없이 변화하는 상황에 맞춰 참신하고 새로운 칩 설계 제작이 가능합니다.

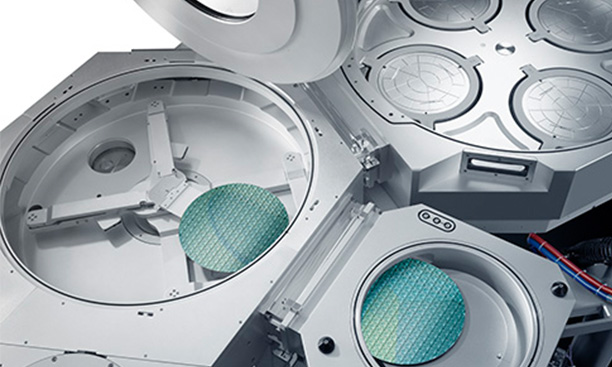

램리서치 과학자와 엔지니어들은 이미 모든 준비를 끝마쳤습니다. 새로운 칩이 팹에 도착했을 때 새로운 공정 기술을 생산에 바로 적용할 수 있도록 말입니다. 박막 증착, 플라즈마 식각, 포토레지스트 제거 및 웨이퍼 세정 부문에서 업계 최고인 램리서치의 광활하고도 강력한 제품 포트폴리오는 반도체 제조 전반의 과정을 보완할 수 있도록 갖춰져 있습니다. 램리서치 제품의 고정밀 질량 계측 시스템 라인도 고급 공정 모니터링과 중요한 공정 제어를 더 디테일하고 전문적으로 지원하는 데 중요한 역할을 합니다.

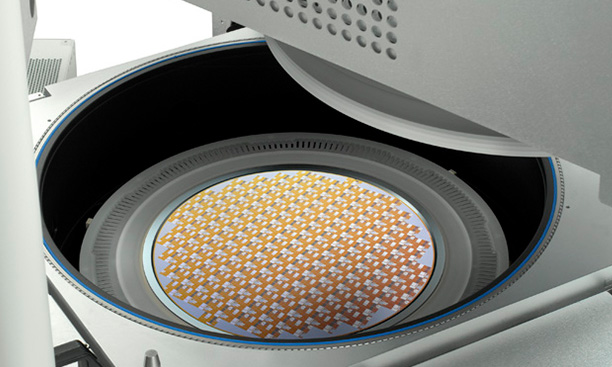

증착(DEPOSITION)

증착 공정에서는 반도체 소자를 만들 때 사용되는 유전(절연) 및 금속(전도) 재료 층을 형성합니다. 재료 유형과 형성 구조에 따라 다양한 기법이 사용됩니다. 전기 화학 증착(Electrochemical deposition, ECD)에서는 소자를 집적 회로에 연결하는 구리 “배선”(배선물질)이 만들어집니다. 실리콘 관통 전극과 웨이퍼 수준의 패키징에는 구리와 기타 금속의 금속 도금도 사용됩니다. 작은 텅스텐 커넥터와 얇은 방지막은 한 번에 단 몇 개의 원자 층만 추가하는 정밀한 화학 기상 증착(chemical vapor deposition, CVD)과 원자층 증착(atomic layer deposition, ALD)을 통해 만들어집니다. 플라즈마 강화 CVD(PECVD), 고정밀 플라즈마 CVD(HDP-CVD) 및 ALD는 이 모든 전기 구조물을 분리하고 보호하는 임계 절연층을 형성할 때 사용합니다.

수많은 재료와 까다로운 피처를 위해 램리서치의 박막 증착 제품은 다양하고 어려운 소자 부문에 필요한 정밀성과 성능, 유연성을 갖췄습니다.

식각(ETCH)

식각 공정은 증착 시에 첨가된 유전(절연) 및 금속(전도) 물질을 선택적으로 제거하여 칩 피처의 형성을 돕습니다. 이러한 공정에서는 여러 종류의 재료를 사용하여 더 작고 복잡하고 길고 가는 피처를 제작해야 합니다. 1차 기술인 반응성 이온 식각(reactive ion etch, RIE)을 통해 웨이퍼 표면에 이온(하전 입자) 충격을 가하여 물질을 제거합니다. 가장 작은 피처일 때는 원자층 식각(ALE)을 통해 원자층을 한 번에 몇 개씩 제거합니다. 전도체 식각 공정은 트랜지스터 같은 중요한 전기 구성요소의 형상을 정밀하게 만들고, 유전체 식각은 전도성 부품을 보호하는 절연 구조물을 만듭니다. 식각 공정에서는 가령 칩을 서로 연결하는 TSV와 미세전자기계시스템(MEMS)에서 사용되는 기다란 기둥 모양의 피처도 만듭니다.

램리서치의 플라즈마 식각 시스템은 가늘고 긴 형상 또는 짧고 넓은 형상 등 몇 나노미터 단위로 측정되는 구조물을 정확하게 만들 때 필요한 고성능, 고생산성 능력을 갖췄습니다.

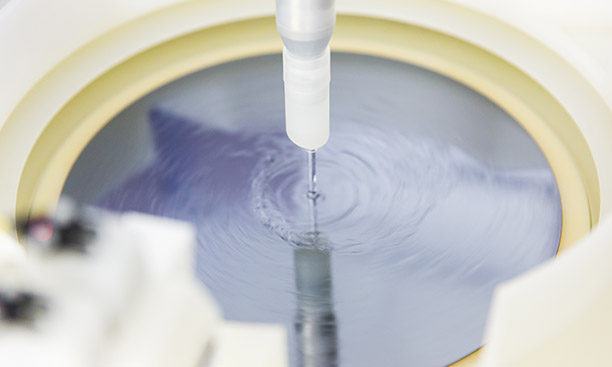

제거 및 세정(STRIP & CLEAN)

제거 및 세정 기법은 나중에 결함의 원인이 될 수도 있는 불필요한 물질을 제조 단계 사이 사이마다 제거하고, 추후 처리를 위해 웨이퍼 표면을 준비하는 데 사용합니다. 포토레지스트 제거 작업을 통해 이온 주입 또는 식각 단계 이후 포토레지스트 필름과 잔여물을 제거합니다. 파티클, 오염물, 잔여물과 기타 불필요한 물질을 제거하기 위하여 제조 과정 전반에 웨이퍼 세정 단계가 들어가 있습니다. 습식 처리 기술은 제거와 식각뿐만 아니라 웨이퍼 세정에도 사용할 수 있습니다. 플라즈마 베벨 세정은 웨이퍼 엣지에서 소자 영역에 영향을 줄 수도 있는 불필요한 물질을 제거하여 수율을 높일 목적으로 사용합니다.

램리서치의 제거 기술은 남아 있는 포토레지스트를 선택적으로 제거하고 여러 용도에 사용할 수 있는 공정 유연성을 갖췄습니다. 한편 램리서치의 고생산성 세정 제품은 까다로운 세정 단계에 사용되어 중심부터 가장자리까지 표면을 깨끗하게 합니다.

질량 계측(MASS METROLOGY)

질량 계측을 통해 증착, 식각, 세정 공정 후 질량의 변화를 측정하여 자주 반복되는 이러한 핵심 제조 단계를 모니터링하고 제어합니다. 박막 스택, 고종횡비(high aspect-ratio) 구조, 복잡한 3D 구조 같은 설계 구성요소의 경우, 광학 기법이라도 두껍거나 깊거나 불투명한 피처를 정확하게 측정하기란 한계가 있습니다. 이 같은 경우일 때 질량 변동을 측정하면, 대체로 변동 허용오차가 거의 없는 고급 소자 구조에서 중요한 피처를 고정밀로 간편하게 모니터링하고 제어할 수 있습니다.

램리서치의 고정밀 질량 계측 시스템 라인은 증착, 식각, 세정 단계의 인라인 모니터링과 제어를 실시간으로 실행합니다. 미세한 질량 변화를 기록하여 잠재적 공정 변화를 정확하게 감지할 수 있습니다.