在原子级尺度上进行精密控制

制造当今最先进的芯片所需的半导体工艺面临着挑战,纳米级特征、新材料和日益复杂的3D结构都需要突破物理和化学的边界。为满足新芯片设计中不断变化的制造需求,必须在原子级尺度上进行精密控制。

为了确保新芯片投入生产时,这些新的工艺技术能满足生产需求,我们的科学家和工程师对客户的生产需求了如指掌。我们提供多种市场领先的产品组合,用于薄膜沉积、等离子刻蚀、光刻胶去胶和晶圆清洗,这些都是在半导体制造的整个过程中互为补充的加工步骤。为了支持先进工艺监测和关键步骤控制,我们的产品组合还包括一系列高精度的质量计量系统。

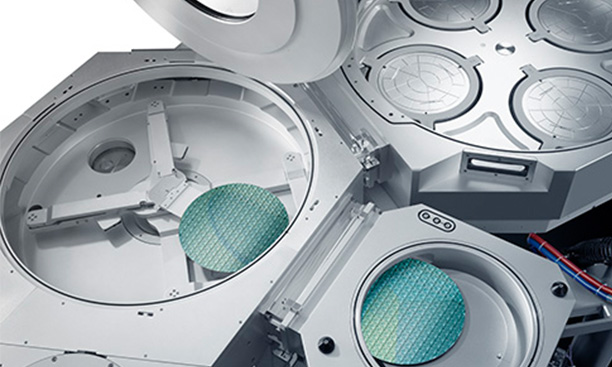

沉积

利用沉积工艺可形成用于构建半导体器件的介电(绝缘)层和金属(导电)材料。依据具体的材料和结构,需要采用不同的技术。利用电化学沉积 (ECD) 可形成连接集成电路中器件的铜“线”(互连)。铜和其他金属的电镀工艺也被用于硅通孔和晶圆级封装应用。微型钨连接器和薄阻挡膜是用精密的化学气相沉积 (CVD) 工艺和原子层沉积 (ALD) 工艺制造的,这两种工艺一次只增加数层原子层。等离子增强化学气相沉积(PECVD)工艺、高密度等离子体化学气相沉积 (HDP-CVD) 工艺和原子层沉积工艺被用于形成隔离和保护所有这些电气结构的关键绝缘层。

对于涉及众多材料和严苛特征的工艺,我们的薄膜沉积产品可提供各种极具挑战性的器件应用所需的精度、性能和灵活性。

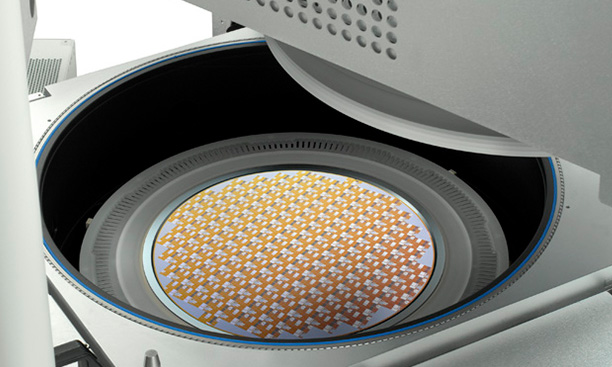

刻蚀

刻蚀工艺通过选择性地移除沉积过程中添加的介电(绝缘)材料和金属(导电)材料,来帮助构建芯片特征。这些工艺涉及使用多种材料制造越来越小、越来越复杂的高窄形特征。采用的主要技术为反应离子刻蚀 (RIE),即用离子(带电粒子)轰击晶圆表面,以移除相应的材料。对于最微小的特征,原子层刻蚀 (ALE) 可以一次只移除数层原子层。导体刻蚀工艺可以精确地形成晶体管等重要电气组件,介电刻蚀工艺则形成保护导电部分的绝缘结构。利用刻蚀工艺还可形成高柱状特征,如硅通孔(用于连接芯片)和微机电系统(MEMS) 中所用的特征。

无论高窄、短宽或是只有几纳米大小,我们的等离子刻蚀设备都能为形成这些精确结构提供必要的高性能和高生产力。

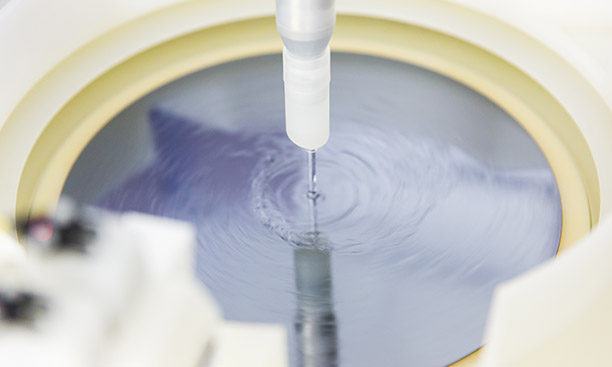

去胶和清洗

在各个制造步骤之间,需要采用去胶和清洗工艺,清除后期可能导致缺陷的无用材料,在晶圆表面做好后续加工的准备。光刻胶去胶工艺在离子植入或刻蚀之后,清除光刻薄膜和残余物。为了清除颗粒、污染物、残余物和其他无用材料,必须在整个制造过程中插入晶圆清洗步骤。湿法加工技术可用于晶圆清洗、去胶和刻蚀应用。等离子边角清洗通过从晶圆边缘清除可能会影响器件面积的无用材料,提高芯片的良率。

我们的去胶技术可选择性地清除残余的光刻胶,工艺灵活性高,适用于多种应用,而针对要求最严苛的清洗步骤,我们具有高生产力的清洗产品使从中心到边缘的表面洁净如新。

质量计量

质量计量技术用于测量质量在沉积、刻蚀和清洗工艺实施之后的变化,从而对这些经常被重复的核心制造步骤实施监测和控制。对于薄膜堆栈、高深宽比结构、复杂的3D架构等设计组件,光学技术能力有限,难以准确测量较厚、较深或非透明的特征。测量这些应用中的质量变化是一种简单直接的高精度解决方案,可以用于监测和控制偏差容忍度极低的先进器件结构中的关键特征。

我们的高精度质量计量系统系列可以实时在线监测和控制沉积、刻蚀和清洗步骤——记录质量的微小变化,对潜在的工艺流程偏差进行先进检测。