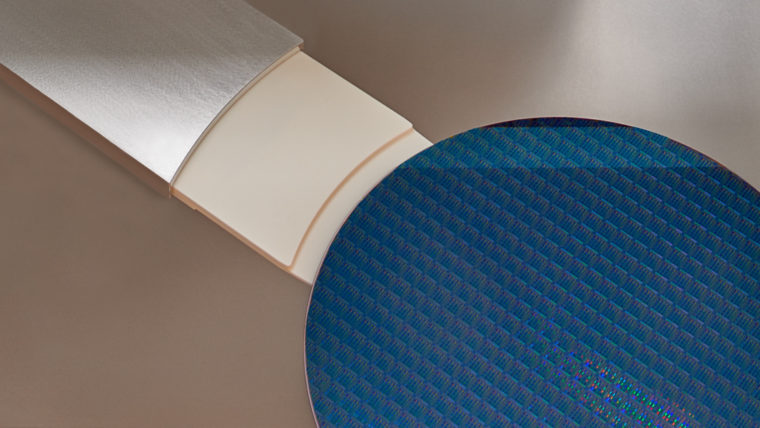

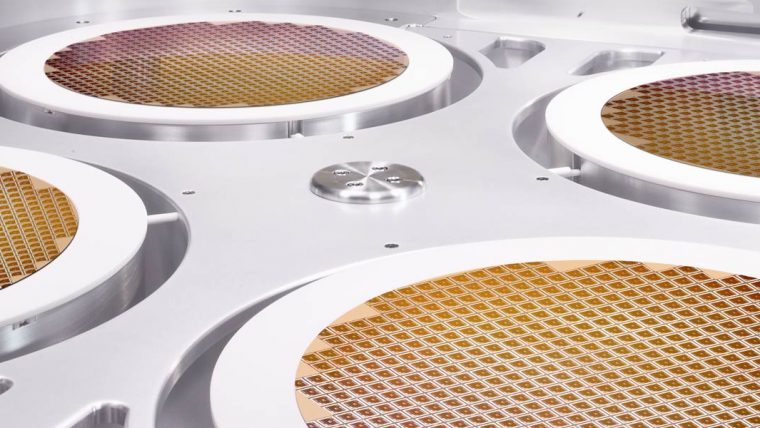

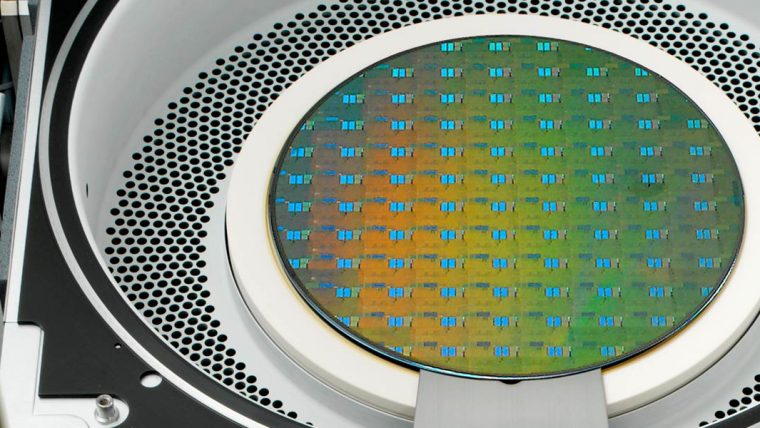

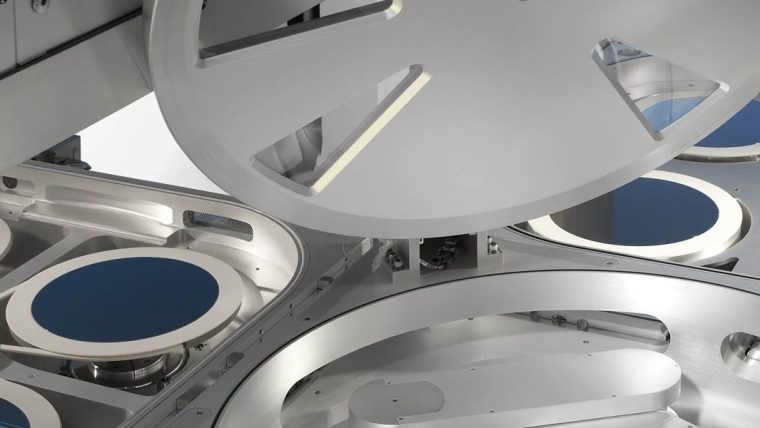

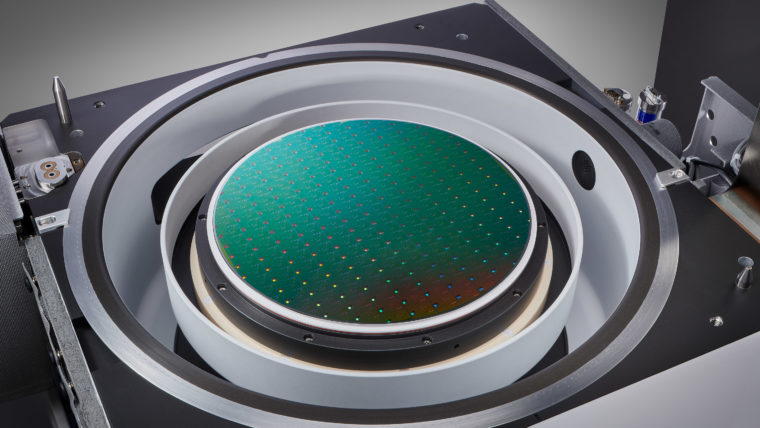

互連構成了複雜的佈線,用來連接晶片上數十億個獨立單元,包括電晶體、電容等。隨著越來越小的元件緊密地放置在一起,因此也需要更多的互連層,這使連結晶片上的所有單元也越來越具挑戰性。事實上,隨著特徵結構尺寸的持續微縮,互連結構已成為現今最先進晶片的速度瓶頸。因此,需要開發能把金屬連接的電阻降至最低的技術以及創新的介電材料,以提升其絕緣能力。為了生產最先進的高效能電子元件,先進的互連結構涉及狹窄的幾何與複雜的薄膜層,需要更靈活、更精密的製程功能來實現。

互連

解決方案Fabtex™ Yield Optimizer

Semiconductor Yield Optimization Platform

Fabtex™ Yield Optimizer is a cutting-edge software platform designed to help semiconductor foundries accelerate yield ramp and improve high-volume manufacturing performance.

Related Blog Posts

-

Will Moly Replace Tungsten in Semiconductors?

Feb 1, 2024To keep pace with Moore's Law and enable greater interconnect scaling, the semiconductor ecosystem is continually experimenting with variations of materials. Tungsten has been the interconnect metal of choice for nearly a quarter century in NAND, DRAM, and logic/foundry middle-of-line applications. But scaling requirements are now pushing the boundaries of what is possible with tungsten. A variety of metals are being considered, but one — molybdenum — is an especially promising candidate. At the atomic dimensions required for advanced chipmaking, moly is emerging as the most suitable material to replace tungsten, creating a major inflection in the industry.

-

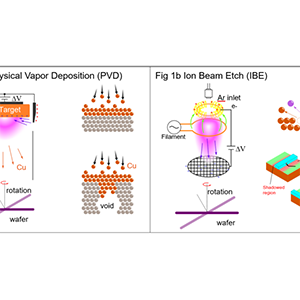

A Deposition and Etch Technique to Lower Resistance of Semiconductor Metal Lines

Mar 22, 2023Cu’s resistivity depends on its crystal structure, void volume, grain boundaries and material interface mismatch, which becomes more significant at smaller scales. The formation of Cu wires is traditionally done by etching a trench pattern in low-k silicon dioxide using a trench etch process, and subsequently filling the trench with Cu via a damascene flow. Unfortunately, this method produces multi-crystalline structures with significant grain boundaries and voids, which increases the Cu wire resistance. A highly resistive TaN liner material is also utilized in this process to prevent Cu diffusion during the damascene annealing process.